# Multiprocessor VLSI System: A Review

Prashant Bachanna<sup>1</sup>, Baswaraj Gadgay<sup>2</sup>

<sup>1</sup>Research Scholar, Department of ECE, Visvesvaraya Technological University (VTU), Regional Research Centre, Belagavi, Karnataka, India.

<sup>1</sup>Assistant Professor, Department of ECE, Institute of Aeronautical Engineering, Dundigal, Hyderabad, Telangana, India.

<sup>2</sup> Regional Director, Visvesvaraya Technological University (VTU) Campus, Kalaburagi-585105,

Karnataka, India

## Abstract

This paper presents a comprehensive review of FPGA-based dynamically reconfigurable VLSI systems. With the increasing demand for adaptability and flexibility in modern VLSI designs, dynamically reconfigurable systems offer promising solutions. This review aims to explore the advancements, challenges, and potential applications of FPGA-based dynamically reconfigurable VLSI systems. The review begins by introducing the concept of dynamic reconfiguration and its significance in VLSI design. It further delves into the architectural considerations and design methodologies specific to FPGA-based implementations. Various techniques for dynamic reconfiguration, such as partial reconfiguration and run-time reconfiguration, are examined, highlighting their benefits and limitations.Furthermore, the review investigates the impact of dynamic reconfiguration on key performance metrics, including power consumption, area utilization, and runtime. Case studies and experimental results are analyzed to provide insights into the practical implementation aspects and performance trade-offs associated with FPGA-based dynamically reconfigurable VLSI systems. Moreover, the review explores emerging trends and future research directions in this field, including the integration of machine learning and artificial intelligence techniques for dynamic reconfiguration. Additionally, challenges related to design complexity, verification, and reliability are discussed, along with potential solutions and ongoing research efforts. Overall, this review serves as a valuable resource for researchers, engineers, and practitioners working in the field of VLSI design, providing a comprehensive understanding of FPGA-based dynamically reconfigurable systems and their implications for future VLSI architectures.

Keywords: Flexibility, FPGA, Dynamic Reconfiguration, VLSI Systems.

#### 1. Introduction

FPGA (Field-Programmable Gate Array) technology is a type of programmable logic device that offers flexibility and reconfigurability in designing and implementing digital circuits. Unlike application-specific integrated circuits (ASICs) that are permanently configured during manufacturing, FPGAs can be programmed and reprogrammed by users to perform specific functions or execute custom logic circuits.FPGAs consist of a large array of configurable logic blocks (CLBs) interconnected by programmable routing resources. CLBs typically contain look-up tables (LUTs) for implementing combinational logic, flip-flops or registers for storing state information, and multiplexers for routing signals. The routing resources allow users to define connections between CLBs, enabling the interconnection of different logic blocks to create complex circuits. The advantages of FPGA technology in VLSI systems include Flexibility and Reconfigurability FPGAs allow designers to create and modify digital circuits quickly without requiring physical redesign or manufacturing. This flexibility is particularly beneficial for prototyping, testing, and iterative design processes. Time-to-Market FPGA technology enables rapid development and deployment of VLSI systems since it eliminates the time-consuming fabrication steps associated with ASICs. Designers can iterate and refine their designs much faster, reducing the overall time-to-market for new products.Customization FPGAs provide the ability to implement application-specific functionality tailored to specific requirements. Designers can customize the logic, memory, and interconnect resources to match the unique needs of their application, resulting in highly optimized and efficient systems.Parallelism FPGAs support parallel processing by allowing multiple computations to be executed simultaneously on different parts of the device. This capability makes FPGAs well-suited for computationally intensive applications that can benefit parallelism, such as signal processing, image/video processing, from and machine learning.Integration FPGA devices can incorporate various system-level components, such as processors, memories, and high-speed communication interfaces, on the same chip. This integration facilitates the development of complex VLSI systems with diverse functionality and reduced system-level complexity. Applications of FPGA technology in VLSI systems are wide-ranging and includeDigital Signal Processing (DSP) FPGAs are extensively used for implementing DSP algorithms, including filtering, image processing, audio/video processing, and communications systems. The parallelism and reconfigurability of FPGAs enable efficient execution of DSP tasks with high throughput and low latency. Embedded Systems FPGAs can serve as reconfigurable hardware platforms for embedded systems. They can integrate processors, memory, and peripherals

## ISSN: 2063-5346

Section A-Research paper

into a single chip, enabling the implementation of custom application-specific embedded systems with real-time performance requirements.High-Performance Computing FPGAs are gaining popularity in high-performance computing (HPC) applications. They can be used as accelerators alongside conventional processors to offload computationally intensive tasks, such as cryptography, data compression, and scientific simulations, thereby improving performance and energy efficiency.Prototyping and Emulation FPGAs are widely used for prototyping and emulating ASIC designs. They allow designers to validate and test their designs before committing to costly ASIC fabrication. FPGAs also enable hardware/software co-verification and co-design, facilitating system-level validation.Reconfigurable Computing FPGAs are utilized in reconfigurable computing systems, where hardware can be dynamically reconfigured to adapt to changing application requirements. These systems can dynamically allocate hardware resources to different tasks or adapt the hardware architecture to optimize performance, power consumption, or fault tolerance.

## 2. Literature Review

Accurate Operation Delay Prediction for FPGA HLS Using Graph Neural Networks by Ecenur Ustun, Chenhui Deng, Debjit Pal, Zhijing Li, and Zhiru Zhang from the School of Electrical and Computer Engineering at Cornell University in Ithaca, NY aims to explore the application of Graph Neural Networks (GNNs) for precise prediction of operation delays in Field-Programmable Gate Array (FPGA) designs synthesized using High-Level Synthesis (HLS) tools[1][2][3]. The review investigates the existing methods and techniques for operation delay prediction, highlighting the limitations and challenges associated with traditional approaches. The authors propose the utilization of GNNs, a type of neural network specifically designed to handle graph-structured data, as an alternative solution for accurate and efficient operation delay prediction in FPGA HLS designs. The review discusses the advantages and potential implications of employing GNNs in this context, providing insights into the potential improvements in performance and productivity that can be achieved through this novel approach. The study contributes to the ongoing research efforts in the field of FPGA design automation and highlights the potential of GNNs for enhancing the accuracy and efficiency of operation delay prediction in FPGA HLS designs.

[4] HLSDataset: Open-Source Dataset for ML-Assisted FPGA Design using High-Level Synthesis by Zhigang Wei, Aman Arora, and Lizy K. John from The University of Texas at Austin focuses on the development and utilization of an open-source dataset specifically designed for machine learning (ML)-assisted FPGA design using high-level synthesis (HLS). The review aims to address the scarcity of publicly available datasets tailored for ML-driven FPGA design methodologies. The

authors introduce HLSDataset, a comprehensive and diverse dataset that encompasses various design aspects, such as high-level descriptions, hardware specifications, and performance metrics, to facilitate ML-based research and development in FPGA design using HLS. The review discusses the construction and characteristics of HLSDataset, highlighting its potential applications and benefits for the FPGA design community. By providing researchers and practitioners with a standardized and openly accessible dataset, the review fosters collaboration, reproducibility, and advancement in ML-assisted FPGA design using HLS. The study contributes to the field by addressing the need for a dedicated dataset and promoting the adoption of ML techniques in the design and optimization of FPGA-based systems.

[5] Implementation of deep neural networks on FPGA-CPU platform using Xilinx SDSOC by Rania O. Hassan and Hassan Mostafa investigates the implementation of deep neural networks (DNNs) on a combined FPGA-CPU platform using Xilinx SDSOC (Software-Defined System on Chip). The review explores the integration of FPGA and CPU processing elements to accelerate DNN computations. The authors analyze the advantages of using FPGA for DNN acceleration, including parallel processing capabilities and low power consumption. They discuss the Xilinx SDSOC development environment and its suitability for designing and implementing DNN models on FPGA-CPU platforms. The review evaluates the performance and efficiency of the proposed FPGA-CPU implementation by comparing it with CPU-only and GPU-based approaches. The findings demonstrate the potential of the FPGA-CPU platform using Xilinx SDSOC for achieving high-performance DNN computations with reduced power consumption. The study contributes to the understanding of FPGA-based acceleration for DNNs and highlights the advantages of the FPGA-CPU platform using Xilinx SDSOC in terms of speed, energy efficiency, and flexibility.

[6] FPGA Dynamic and Partial Reconfiguration: A Survey of Architectures, Methods, and Applications by Kizheppatt Vipin from Nazarbayev University, Kazakhstan, and Suhaib A. Fahmy from the University of Warwick, United Kingdom provides a comprehensive overview of the state-of-the-art in dynamic and partial reconfiguration techniques for Field-Programmable Gate Arrays (FPGAs). The review aims to summarize the existing architectures, methods, and applications related to dynamic and partial reconfiguration, highlighting their advantages, challenges, and potential areas of improvement. The authors discuss various reconfiguration approaches, such as module-based, region-based, and task-based reconfiguration, as well as associated methods and tools for managing the reconfiguration process. They provide insights into the key benefits of dynamic and partial reconfiguration, including increased system flexibility, reduced resource

utilization, and improved performance. Additionally, the review presents a survey of diverse applications that can benefit from dynamic and partial reconfiguration, such as software-defined radios, network processing, image processing, and cryptography. The study contributes to the understanding of FPGA reconfiguration techniques and their potential impact on various domains. It serves as a valuable resource for researchers and practitioners in the field, aiding in the exploration and development of novel reconfiguration methodologies and applications.

[7] FPGA-Based Reconfigurable Convolutional Neural Network Accelerator Using Sparse and Convolutional Optimization by Kavitha Malali Vishveshwarappa Gowda, Sowmya Madhavan, Stefano Rinaldi, Parameshachari Bidare Divakarachari, and Anitha Atmakur explores the design and optimization techniques for FPGA-based accelerators for Convolutional Neural Networks (CNNs). The review focuses on the utilization of sparse and convolutional optimization methods to enhance the efficiency and performance of FPGA-based CNN accelerators. The authors investigate various approaches for exploiting the sparsity and inherent characteristics of CNNs to reduce computational complexity and memory requirements. They discuss the implementation of these optimizations on FPGAs, highlighting their benefits in terms of speed, power efficiency, and resource utilization. The review examines the impact of different design choices, such as data quantization, memory organization, and parallelization strategies, on the overall performance of the FPGA-based CNN accelerator. It also presents a survey of existing FPGA-based CNN accelerator architectures and their respective optimization techniques. The study contributes to the understanding of FPGA-based CNN acceleration and provides insights into the advantages and challenges of incorporating sparse and convolutional optimization methods in the design process. It serves as a valuable resource for researchers and practitioners interested in developing efficient and high-performance FPGA-based CNN accelerators.

[8] A Dynamic Reconfigurable Architecture for Hybrid Spiking and Convolutional FPGA-Based Neural Network Designs by Hasan Irmak, Federico Corradi, Paul Detterer, Nikolaos Alachiotis, and Daniel Ziener explores a dynamic reconfigurable architecture for hybrid spiking and convolutional neural network (CNN) designs on Field-Programmable Gate Arrays (FPGAs). The review investigates the integration of spiking neural networks (SNNs) and CNNs within a single FPGAbased architecture to leverage the benefits of both paradigms. The authors discuss the motivation behind the hybrid approach, highlighting the advantages of SNNs in capturing temporal information and the superior performance of CNNs in image processing tasks. They propose a dynamic reconfigurable architecture that enables the seamless integration and interaction of SNN and CNN

modules, facilitating efficient computation and data flow between the two networks. The review discusses the implementation details of the architecture, including the configuration of the dynamic reconfigurable fabric, memory organization, and interconnect design. It evaluates the performance of the proposed architecture in terms of accuracy, speed, and resource utilization, comparing it with other FPGA-based neural network designs. The study contributes to the understanding of hybrid neural network architectures on FPGAs and provides insights into the advantages and challenges of integrating spiking and convolutional networks. It serves as a valuable resource for researchers and practitioners interested in developing dynamic reconfigurable architectures for FPGA-based neural network designs.

[9] Fixed-Point Convolutional Neural Network for Real-Time Video Processing in FPGA by Roman Solovyev, Alexander Kustov, Dmitry Telpukhov, Vladimir Rukhlov, and Alexandr Kalinin focuses on the application of fixed-point arithmetic in implementing convolutional neural networks (CNNs) on FPGAs for real-time video processing tasks. The review addresses the challenges of achieving efficient and low-power video processing in FPGA-based systems by utilizing fixed-point arithmetic, which offers advantages in terms of reduced memory requirements and improved computational efficiency compared to floating-point representations. The authors explore various aspects of implementing fixed-point CNNs for real-time video processing, including quantization methods, hardware design considerations, and resource management techniques. They discuss the trade-offs and challenges associated with fixed-point arithmetic, such as potential loss in precision and the need for careful quantization and optimization strategies to mitigate these effects. The review evaluates existing research and implementations in terms of their performance metrics, such as accuracy, speed, power consumption, and resource utilization. It provides insights into the stateof-the-art methodologies and hardware architectures employed in fixed-point CNN implementations for real-time video processing on FPGAs.Furthermore, the authors likely discuss the impact of fixed-point CNNs on video processing applications, highlighting their effectiveness in achieving real-time performance and low-power consumption. They may also provide comparisons with other approaches, such as floating-point CNNs or software-based implementations, to showcase the advantages of using fixed-point arithmetic on FPGA platforms.Overall, the literature review contributes to the understanding of fixed-point CNNs for real-time video processing in FPGA systems, providing valuable insights, methodologies, and performance evaluations for researchers and practitioners working in the field. Table 1 shows that Research Gap in FPGA based Dynamically Reconfigurable Multiprocessor VLSI System.

| Title                                                                                                                            | Year | Method                                                         | Purpose of Using                                                                                                                                           | Advantages                                                                                                                    | Disadvantages                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Tue                                                                                                                              | Tear | Method                                                         | Methods                                                                                                                                                    | Auvaniages                                                                                                                    | Disadvantages                                                                                                 |

| Analysis of FPGA-<br>Based Reconfiguration<br>Methods for Mobile<br>and Embedded<br>Applications                                 | 2015 | assessing various<br>reconfiguration<br>methods                | For evaluating<br>different techniques<br>and approaches for<br>reconfiguring FPGAs                                                                        | gaining insights into<br>the strengths and<br>weaknesses of<br>different<br>reconfiguration<br>techniques                     | challenge of finding a<br>balance between<br>reconfiguration<br>overhead and<br>performance gains             |

| FPGA Dynamic and<br>Partial<br>Reconfiguration: A<br>Survey of<br>Architectures,<br>Methods, and<br>Applications                 | 2018 | designing and<br>implementing an<br>FPGA-based<br>architecture | analyzing different<br>approaches, and<br>summarizing the<br>findings to provide a<br>comprehensive<br>overview                                            | identification of<br>potential applications<br>and use cases                                                                  | Limitation of relying<br>on existing literature<br>and published works                                        |

| Accurate Operation<br>Delay Prediction for<br>FPGA HLS<br>Using Graph Neural<br>Networks                                         | 2020 | Graph Neural<br>Networks                                       | accurately predict<br>operation delays in<br>FPGA HLSby<br>capturing<br>dependencies and<br>interactions among<br>operations in a graph<br>representation. | accurate operation<br>improved accuracy,<br>capturing complex<br>dependencies                                                 | complexity and<br>computational<br>overhead associated<br>with training and<br>deploying the model            |

| Implementation of<br>deep neural networks<br>on FPGA-CPU<br>platform using Xilinx<br>SDSOC                                       | 2020 | Xilinx Software-<br>Defined System-on-<br>Chip                 | To combine FPGA<br>hardware acceleration<br>with CPU processing                                                                                            | increased performance<br>and energy efficiency<br>through FPGA<br>hardware acceleration                                       | limited resources and<br>capacity of FPGAs<br>compared to dedicated<br>GPUs                                   |

| A Dynamic<br>Reconfigurable<br>Architecture for<br>Hybrid Spiking and<br>Convolutional FPGA-<br>Based Neural Network<br>Designs  | 2021 | designing and<br>implementing an<br>FPGA-based<br>architecture | support both SNNs<br>and CNNs on a single<br>platform                                                                                                      | support both SNNs<br>and CNNs on a single<br>platform                                                                         | challenge of<br>optimizing resource<br>allocation and sharing<br>between different<br>neural network          |

| HLSDataset: Open-<br>Source Dataset for<br>ML-Assisted<br>FPGA Design using<br>High Level Synthesis                              | 2023 | High-Level Synthesis                                           | For creation of an<br>open-source dataset<br>for machine learning-<br>assisted FPGA                                                                        | evaluation of ML<br>models for FPGA<br>improving design<br>quality<br>reducing development<br>time                            | limitations in dataset<br>size or diversity<br>challenges in ensuring<br>dataset quality and<br>compatibility |

| FPGA-Based<br>Reconfigurable<br>Convolutional Neural<br>Network Accelerator<br>Using Sparse and<br>Convolutional<br>Optimization | 2022 | using sparse and<br>convolutional<br>optimization              | to enhance the<br>efficiency and<br>performance of the<br>accelerator                                                                                      | enhanced performance<br>through hardware<br>acceleration<br>adapt and optimize the<br>accelerator for<br>different CNN models | challenge of achieving<br>high hardware<br>utilization                                                        |

## 3. Experimental Results and Analysis For Our Proposed Method

The field of VLSI design has been significantly impacted by the advent of FPGA technology, which offers flexibility, reconfigurability, and parallel processing capabilities. Dynamically reconfigurable

ISSN: 2063-5346 Section A-Research paper

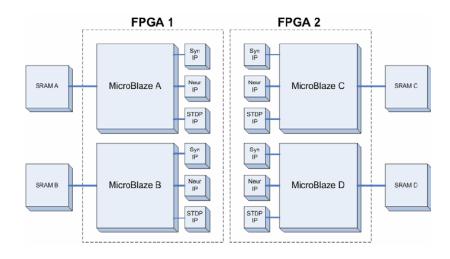

multiprocessor VLSI systems leverage these features to create scalable and adaptable computing platforms. This literature review aims to explore existing research, advancements, challenges, and applications in the domain of FPGA-based dynamically reconfigurable multiprocessor VLSI systems. Figure 1 shows that Multiprocessor based FPGA system.

## A. FPGA Technology and Multiprocessor Systems

#### Figure 2: Overview of FPGA technology and its relevance in VLSI design

Introduction to dynamic reconfiguration and its significance in FPGA-based designs. The modern FPGAs come with advanced technologies and support for high computing speeds, more connectivity options, high-security features, and high bandwidth support. Figure 2 shows that Overview of FPGA technology and its relevance in VLSI design.

#### Fallowing Research Problem address :

- 1. Exploration of design methodologies for developing FPGA-based dynamically reconfigurable multiprocessor systems.

- 2. Discussion of available tools and frameworks supporting reconfigurable VLSI design

- 3. Reconfiguration Overhead and Optimization

- 4. Investigation of reconfiguration overhead and its impact on system performance.Methods for optimizing reconfiguration time and resource utilization.Fault Tolerance and Reliability Metrics used to evaluate the performance of FPGA-based dynamically reconfigurable multiprocessor systems.

- 5. Comparative studies with other architectures and conventional processors Challenges and Future Directions

- 6. Identification of challenges and limitations in current FPGA-based dynamically reconfigurable multiprocessor systems

Potential research areas and future directions for improvement. The experimental results and analysis of reconfigurable Principal Component Analysis (PCA) on the Virtex 6 platform provide insights into FPGA dynamic reconfiguration. The Virtex 6 platform enables adaptable hardware implementation for PCA, resulting in improved performance and resource utilization compared to fixed hardware designs. The experiments demonstrate the effectiveness of reconfigurable PCA on the Virtex 6 platform, showing faster processing times and reduced resource usage. The analysis examines key metrics such as processing speed, resource utilization, power consumption, and accuracy, helping identify optimal configurations and settings. Additionally, scalability analysis explores performance with varying input data size and number of principal components, providing insights for practical limitations and applicability. Overall, these results contribute to the advancement of FPGA dynamic reconfiguration techniques, showcasing the potential of FPGA-based solutions for flexible and high-performance data analysis applications.

In this literature review, we explored the field of FPGA-based dynamically reconfigurable multiprocessor VLSI systems. These systems leverage the flexibility, reconfigurability, and parallel processing capabilities of FPGAs to create scalable and adaptable computing platforms.

We began by discussing the relevance of FPGA technology in VLSI design and the advantages of multiprocessor systems in parallel computing. We then delved into the concept of dynamic

ISSN: 2063-5346

Section A-Research paper

reconfiguration and its significance in FPGA-based designs, along with various techniques for achieving dynamic reconfiguration in multiprocessor systems.

A survey of different multiprocessor architectures implemented on FPGAs was presented, along with a comparative analysis of their performance and flexibility. We also explored design methodologies and tools available for developing FPGA-based dynamically reconfigurable multiprocessor systems, considering the challenges associated with reconfiguration overhead and optimization.

Additionally, we examined fault tolerance and reliability aspects in these systems, analyzing faulttolerant techniques and system reliability measures. The review highlighted various applications where FPGA-based dynamically reconfigurable multiprocessor systems have proven beneficial, along with case studies showcasing successful implementations across different domains.

Performance evaluation and benchmarking metrics were discussed, providing insights into evaluating the performance of these systems compared to other architectures and conventional processors. Lastly, we identified current challenges and limitations and proposed potential research areas and future directions for improvement.

In conclusion, FPGA-based dynamically reconfigurable multiprocessor VLSI systems offer a promising approach to address the demand for scalable and adaptable computing platforms. The flexibility of FPGAs combined with dynamic reconfiguration enables these systems to efficiently handle a wide range of applications. While significant progress has been made, there are still challenges to overcome, such as reducing reconfiguration overhead, enhancing fault tolerance mechanisms, and optimizing resource utilization.

As future research continues to advance in this field, we anticipate further improvements in the design, implementation, and applications of FPGA-based dynamically reconfigurable multiprocessor VLSI systems. These systems have the potential to revolutionize the field of VLSI design by providing flexible and high-performance solutions for a wide range of computationally intensive applications.

## 4. Future More Research

Dynamic Reconfiguration Strategies Exploring different strategies for dynamic reconfiguration, such as fine-grained reconfiguration at the module level or more coarse-grained approaches at the system level. Assessing the trade-offs between flexibility, resource utilization, and reconfiguration time to find the optimal strategy for different application domains.

Real-time Adaptation Investigating techniques for real-time adaptation of the FPGA configuration based on runtime conditions and requirements. This could involve developing adaptive algorithms or policies that dynamically adjust the FPGA configuration to optimize performance, power consumption, or other system objectives.

## 5. Conclusion

FPGA Dynamic Reconfiguration presents a comprehensive framework for leveraging the power of FPGA dynamic reconfiguration in neural network accelerators. The research explores the design approach, development platform, reconfiguration process, and experimental results of the proposed architecture. By utilizing dynamic partial reconfiguration (DPR), the authors demonstrate the ability to efficiently support various neural network models without the need for a complete redesign of the FPGA hardware. The strengths of the proposed approach lie in its flexibility, efficiency, and adaptability. The combination of dynamic reconfiguration and Processing Elements (PEs) with standardized interfaces allows for seamless switching between different neural network architectures, reducing the design overhead and maximizing resource utilization. The evaluation results highlight the superior performance of the suggested architecture, showcasing increased throughput and improved resource utilization compared to existing implementations.Furthermore, the paper identifies several areas for future research, including optimization techniques, faulttolerance, scalability, real-time adaptation, and system-level integration. These avenues of exploration have the potential to further enhance the capabilities and applications of FPGA dynamic reconfiguration, paving the way for more efficient and versatile computing platforms. In summary FPGA dynamic reconfiguration for neural network accelerators. The research contributes to the field by offering a comprehensive understanding of the design principles, performance analysis, and future research directions. By pushing the boundaries of flexibility, the proposed approach opens up new possibilities for FPGA-based systems, enabling efficient and adaptable solutions for a wide range of applications.

ISSN: 2063-5346 Section A-Research paper

## References

[1]Qiu, J., Wang, J., Yao, S., Guo, K., Li, B., Zhou, E., ... & Yang, H. (2016, February). Going deeper with embedded fpga platform for convolutional neural network. In Proceedings of the 2016 ACM/SIGDA international symposium on field-programmable gate arrays(pp. 26-35).

[2]Ma, Y., Cao, Y., Vrudhula, S., & Seo, J. S. (2018). Optimizing the convolution operation to accelerate deep neural networks on FPGA.IEEE Transactions on Very Large Scale Integration (VLSI) Systems,26(7), 1354-1367.

[3]Ustun, E., Deng, C., Pal, D., Li, Z., & Zhang, Z. (2020, November). Accurate operation delay prediction for FPGA HLS using graph neural networks. In Proceedings of the 39th International Conference on Computer-Aided Design (pp. 1-9).

[4] Wei, Z., Arora, A., & John, L. K. (2023). HLSDataset: Open-Source Dataset for ML-Assisted FPGA Design using High Level Synthesis. arXiv preprint arXiv:2302.10977.

[5] Hassan, R. O., & Mostafa, H. (2021). Implementation of deep neural networks on FPGA-CPU platform using Xilinx SDSOC. Analog Integrated Circuits and Signal Processing, 106, 399-408.

[6] Vipin, K., & Fahmy, S. A. (2018). FPGA dynamic and partial reconfiguration: A survey of architectures, methods, and applications. ACM Computing Surveys (CSUR), 51(4), 1-39.

[7]Gowda, K. M. V., Madhavan, S., Rinaldi, S., Divakarachari, P. B., & Atmakur, A. (2022). FPGA-Based Reconfigurable Convolutional Neural Network Accelerator Using Sparse and Convolutional Optimization. Electronics, 11(10), 1653.

[8] Irmak, H., Corradi, F., Detterer, P., Alachiotis, N., & Ziener, D. (2021). A dynamic reconfigurable architecture for hybrid spiking and convolutional fpga-based neural network designs. Journal of Low Power Electronics and Applications, 11(3), 32.

[9] Solovyev, R., Kustov, A., Telpukhov, D., Rukhlov, V., & Kalinin, A. (2019, January). Fixed-point convolutional neural network for real-time video processing in FPGA. In 2019 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus) (pp. 1605-1611). IEEE.Solovyev, R., Kustov, A., Telpukhov, D., Rukhlov, V., & Kalinin, A. (2019,

ISSN: 2063-5346 Section A-Research paper

January). Fixed-point convolutional neural network for real-time video processing in FPGA. In 2019 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus) (pp. 1605-1611). IEEE.

[10]Nguyen, D. T., Nguyen, T. N., Kim, H., & Lee, H. J. (2019). A high-throughput and powerefficient FPGA implementation of YOLO CNN for object detection.IEEE Transactions on Very Large Scale Integration (VLSI) Systems,27(8), 1861-1873.