# Design and Implementation of an XOR Based 16-bit Carry Select Adder for Area, Delay and Power Minimization

Dr. Nookala Venu

Assistant Professor, Internet of Things (IoT), Offered by Department of IT, Madhav Institute of Technology & Science, Gwalior - 474 005, Madhya Pradesh, India, (A Govt. Aided UGC Autonomous Institute). venunookala@mitsgwalior.in

| Article History: | Received: 24.07.2023 | Revised:06.08.2023 | Accepted: 03.09.2023 |

|------------------|----------------------|--------------------|----------------------|

## Abstract

In different types of processors and other digital circuits adders are most widely used. Low power and area efficient high-speed circuits are most substantial area in the research of VLSI design. The carry select adder is one of the fast adders which has less area and reduced power consumption. In this paper, a 16-bit carry select adder has been presented using modified XOR based full adder to reduce circuit complexity, area and delay. The modified full adder design requires only two XOR gates and one multiplexer. The modified 16-bit carry select adder gives better result than conventional carry select adder with respect to area, power consumption and delay.

Keywords: Low Power, Area Efficient, XOR based Adder, Carry select Adder.

# DOI: 10.48047/ecb/2023.12.9.142

# 1. Introduction

In digital integrated circuit design, addition is the heart of computer arithmetic. It has special significance in processors and many other digital circuits. In rapidly growing mobile industry faster units, smaller area and less power become major concern. For increasing portability of mobile electronics, area and power are the key factors [1-2]. They also major concern to increase battery life. In VLSI system, reduction in area and power are the main focus point of research. Faster speed for addition and multiplication is a fundamental requirement of high-performance processors. Arithmetic units are the work horse of a computational circuit and addition is the heart of this. In VLSI sub system the power efficient and high-performance adders are most desired digital circuit. Speed of adder is usually limited for carry propagation bit. The sum of each bit in an adder is generated sequentially after the addition of previous bit and a carry propagated to the next position [3-4]. There are plenty of adder designs available

in the literature such as Ripple Carry Adder (RCA), Carry Look Ahead Adder (CLA), Carry Select Adder (CSA), Carry Skip Adder which have their own advantages and disadvantages. CSA is one of the fastest adders because of its less area and power consumption. In CSA there are two multiplexed RCA which act in parallel assuming carry in, Cin = 0 and in other Cin = 1, then final sum is selected through multiplexer [5-8]. In conventional CSA, XOR, AND and OR gate based full adders are used. These adders consumes more area in the chip due to large number of transistors are used in these gates, the delay is higher and consumes more power. In the present work, XOR based modified full adder have been used as the building blocks of the modified CSA to reduce area, delay and power consumption. The layout of the 16-bit CSA is designed in Micro wind software [9-14]. The results obtained from the layout data is compared with the conventional CSA. In digital integrated circuit design, adders are among the most common building blocks of microprocessor processors. You can't have DSP programmes without them. Researchers have attempted, and continue to attempt, to create adders that provide fast speed, low power consumption, reduced area, or some combination of these benefits as technology progresses. There is a carry value that is produced by each adder in an arithmetic sequence and must be passed on to the next adder in the sequence. As a result, this significantly lengthens the circuit's critical route delay [15-23]. There is less delay in the circuit if the carry is propagated across fewer stages. The necessary total is determined using a multiplexer. Adders can be treated as building blocks of the arithmetic component. For the operations like complementing, decoding and encoding adders are used. Generally, addition involves adding of two numbers which generates sum and carry. All adder architectures either simple or complex are constructed by using fundamental blocks which are half adder and full adder. For small number of bits, simple adders like ripple carry adder, carry look ahead adders are sufficient [24-29]. However, delay increases as the bits number increases because of the passing of the carry to the next stage. So, we use Parallel Prefix Adders to perform arithmetic operations on large number of bits. Parallel prefix adders are high speed adders and take small area and give less delay. These adders consume low power and relatively take less area on chip. Primary concern of adders is speed and later we have chip area and power consumption of adder [30-34].

#### 2. Literature Review

FPGAs are susceptible to soft errors (SEs), although there are ways to protect against or identify them. Data cleaning is one example (DS) Scanning the entire device's memory at regular intervals to fix any problems found is the essence of DS. To replace the corrupted frames, you need to save the original configuration data or at least a portion of it. However,

Eur. Chem. Bull. 2023, 12( issue 9), 256-269

as ECC codes can only correct a single bit or two neighboring bits in a frame, including ECC bits in every frame of the FPGA bit stream may not be enough [35-41]. Bit stream security is provided by both ECC and cyclic redundancy check (CRC) codes; however the latter are only effective for integrity checks and not error repair. Another popular approach to improving dependability and spotting SEs is the use of triple module redundancy (TMR) in conjunction with a voter mechanism. Even though this technique greatly extends the MTTF, it also triples the area and power requirements compared to the pioneering design [42-48]. The snake is an essential element in every modern area. In this digital age, everyone is working on miniaturization. The three main aspects of design, namely, area, power consumption and delay need to achieve optimal balance. Because helpers have been used as a key component of complex digital networks, increasing the performance of digital providers will accelerate the speed of binary operations in such complex zones [49-54].

A good VLSI model is a design with small footprints and quick surgery. According to Moore's law, as the number of transistors in a chip increases, so does the overall chip area. In VLSI design, it is important to improve the Area and Delay parameters. The field of Very Large-Scale Integration (VLSI) design; circuit summing is one of the most widely used data transmission architectures [55-59]. With the advancement of VLSI technology, research is emerging to design low-speed, high-speed, small-area, or combination of two architectures. The design of ads implemented through memristor. Explains the memristor-based design for standard ad architectures (ripple-bearing adder, bearing adder, and corresponding prefinder adder). Compare area and waiting time [60-63]. Surprisingly, the Radix-2 CLA has the same complexity as the parallel adder prefect. The results show that in the adjacent price adder, the Kogge-Stone design has the best metrics for latency and area. An effective insect repellent design, which uses a multiplexer-based multiplexer design rather than using a snake-bearing wound, but an improved enhancer Replace the ripple bearing snake for effective results. Using this improved snake can reduce power consumption and reduce gate delays [64-68]. The proposed proposal is to carry and store oil from 8-bit to 64-bit. With today's digital technology system, which is the most widely used 64-bit format? Since ripple-carrying snakes are one of the most common types of auxiliaries used in many forms, there is a prolonged delay in propagation and consuming more area and energy. Single-bit full-adders are cascaded for construction of the ripple carry adder [69-74]. Each full-adder prior carrying-out signals is ready in the RCA, then only begins its computation. In a carrying ripple adder, the carry-out propagation direction, therefore, specifies the critical path delay. As shown in Figure 1, for a full-adder N-bit, the essential paths in the full-adders are N-bit

carrying propagation paths. The delay time in the N- bit RCA increases linearly as the N-bit increases [75-78].

All modern processors, including microprocessors and digital signal processors, have an arithmetic logic unit (ALU). The computational performance of these modern processors depends on the success of the ALU. The serpent is the foundation stone of the ALU which performs arithmetic and logical work [79-80]. Existing helpers (such as half helpers, full helpers, ripple converters, skip carry assistants and pre-loaders) cannot respond to improvement goals, so this paper offers four types of introductions. Evaluates the decrease in conventional power consumption by lending collectors - money at low voltage and analyses the effects of the difference between the effectiveness of the ripple bear adder (RCA) and the adder te-save-adder (BSA). A higher rate of deferral and the provision of technological means to enhance the BSA's adaptability to change [81-82]. In addition to discussing the effectiveness of power reduction in snakes, this article also delves into the concept of so-called pipelines and the typical methods used to obtain currency.

#### 3. Description of the Proposed Scheme

#### 3.1 XOR Based Full Adder

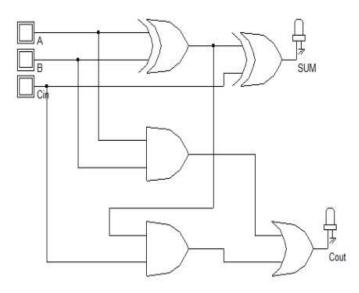

A full adder which is the main building block of n-bit adders gives the result of addition with output carry taking input carry in to consideration. So, actually a one-bit full adder adds three one-bit numbers A, B, and Cin where A and B are the operands, and Cin is a bit carried in from the previous less-significant stage. A conventional full adder implementation based on basic logic gates is shown in Fig. 1.

Fig.1: Conventional 1-bit full adder

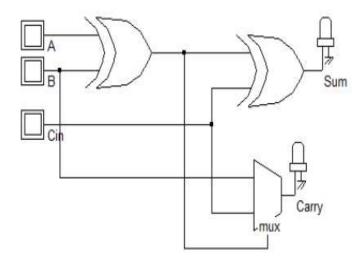

A binary full adder realization employing two XOR gates and one 2:1 MUX is shown in Fig. 2. The layout of conventional and XOR based 1-bit full adder are shown in Fig. 3 and Fig. 4 respectively. The advantage of XOR based adder is that it requires smaller number of transistors.

Fig.2: XOR based 1-bit Full Adder

The main difference between the conventional and XOR based adders is that in XOR based adder other than two XOR gates only one 2:1 MUX is used which needs only 6 MOSFETs where as in conventional type adder other than two XOR gates two AND gates and one OR gate is needed which requires at least 18 number of MOSFETs. So, there is at least 12 numbers of MOSFET savings in XOR based 1-bit adders than conventional which in turn has less area and power consumption at the same time there is also a better delay performance.

#### **3.2 Carry Select Adder**

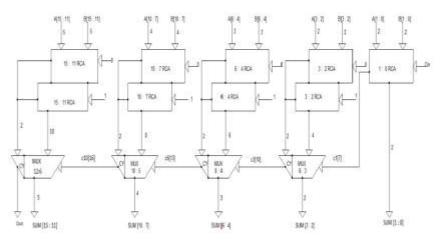

The CSA is constructed from two RCAs and a multiplexer. Addition of two n-bit numbers with CSA is nothing but adding two numbers taking input carry first as zero then using another adder taking input carry as one. After calculation of the two results depending on the correct carry-in the correct sum as well as the correct carry-out is selected with the multiplexer connected at last to get the final output. The structure of a 16-bit CSA is shown in Fig. 5.

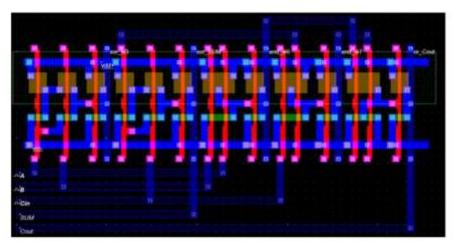

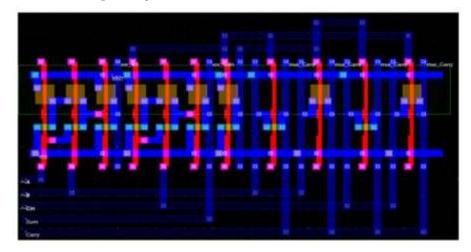

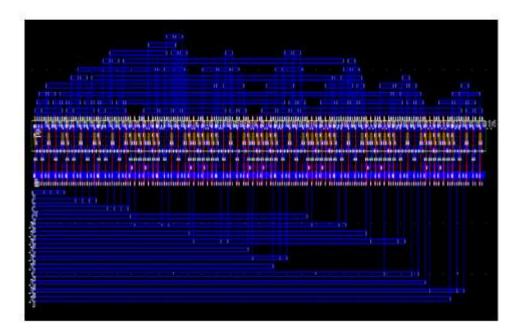

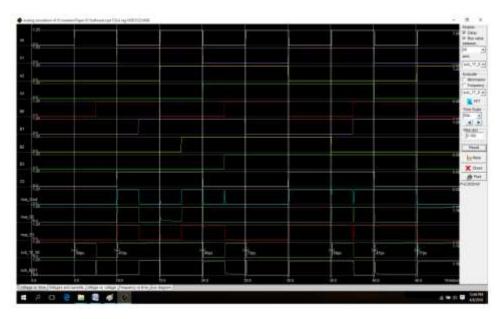

A 16-bit CSA consists of 16-full adders with the carry signal that ripples from one full adder stage to the next, i.e. from LSB to MSB. The layout and input-output wave shapes of a 4-bit CSA are shown in Fig. 6 and Fig. 7 respectively. Due to clarity of the pictures, layout and input output waves of 4-bit CSA are given here in place of 16-bit adder. Results of 16-bit CSA will be given later. Since XOR based 1-bit adders have been used in the 16-bit CSA

which are the main building blocks so the number of MOSFETs required is much less than conventional CSA.

Fig.3: Layout of conventional 1-bit full adder

Fig.4: Layout of XOR based 1-bit full adder

Fig.5: 16-bit carry select adder

Fig.6: Layout of 4-bit carry select adder

Fig.7: Input-output wave shapes of a 4-bit carry select adder

### 4. Results and Discussion

The schematic circuit of the CSA has been designed using DSCH 3.1 simulator and synthesized using 90 nm CMOS technology. The layout was constructed from the Verilog file which is generated from the DSCH software. The obtained power, area and delay information of the adder is from Micro wind layout simulation.

Table I shows the simulation results of both conventional and modified CSA (using XOR based adder) in terms of power, area, delay and power delay product (PDP). Every individual

cell in the design adds to the aggregate cell zone and total power is the sum of leakage power, switching power and static power. The XOR-based circuit has the power reduction for 4-bit, 8-bit and 16-bit are 12.5%, 16.67% and 20.04% respectively. Similarly percentage reduction in area are 1.35%, 6.6% and 9.41% respectively. There is also a delay reduction of 0.8%, 1.3%, and 2.01% respectively. In Table II, gate count and Idd values are shown for 4-bit, 8-bit and 16-bit CSA respectively. In Table III, power, delay and area for 8-bit and 16-bit adders are compared with Reference.

| TABLE L     | COMPARISON OF POWER      | AREA AND DELAY BETWEEN CONVENTIONAL | CSA AND XOR BASED CSA    |

|-------------|--------------------------|-------------------------------------|--------------------------|

| IT IDELL I. | communication of roming, | AREA AND DELAT DETWEEN CONVENTIONAL | CONTAIND MORE DADED CONT |

| Bit size | Adder                | Power (mW) | Area (µm <sup>2</sup> ) | Delay (ns) | PDP (pWSec) |

|----------|----------------------|------------|-------------------------|------------|-------------|

| 4-Bit    | Conventional CSA     | 0.232      | 287.00                  | 2.561      | 0.594       |

|          | XOR based CSA        | 0.203      | 283.12                  | 2.538      | 0.515       |

|          | Percentage reduction | 12.5%      | 1.35%                   | 0.8%       | 13,29%      |

| 8-Bit    | Conventional CSLA    | 0.300      | 580.855                 | 2.520      | 0.756       |

|          | XOR based CSA        | 0.250      | 542.485                 | 2.487      | 0.622       |

|          | Percentage reduction | 16.67%     | 6.6%                    | 1.3%       | 17.72%      |

| 16-Bit   | Conventional CSLA    | 2.803      | 1170.14                 | 5.117      | 14.34       |

|          | XOR based CSA        | 2.241      | 1060.01                 | 5.014      | 11.24       |

|          | Percentage reduction | 20.04%     | 9.41%                   | 2.01%      | 21.62%      |

TABLE II. COMPARISON OF GATE COUNT, IDD MAX AND IDD AVG BETWEEN CONVENTIONAL CSA AND XOR BASED CSA

| Bit size | Adder                | Gate count |        |        | I <sub>dd</sub> max | I <sub>dd</sub> avg |

|----------|----------------------|------------|--------|--------|---------------------|---------------------|

|          |                      | nMOS       | pMOS   | Total  | (mA)                | (mA)                |

| 4-Bit    | Conventional CSA     | 99         | 99     | 198    | 1.679               | 0.193               |

|          | XOR based CSA        | 63         | 63     | 126    | 1.389               | 0.169               |

|          | Percentage reduction | 36.37%     | 36.37% | 36.37% | 17.28%              | 15.54%              |

| 8-Bit    | Conventional CSA     | 195        | 195    | 390    | 2.231               | 0.550               |

|          | XOR based CSA        | 123        | 123    | 246    | 2.132               | 0.459               |

|          | Percentage reduction | 36.93%     | 36.93% | 36.93% | 4.44%               | 16.55%              |

| 16-Bit   | Conventional CSA     | 386        | 386    | 772    | 6.626               | 2.336               |

|          | XOR based CSA        | 243        | 243    | 486    | 5.023               | 2.316               |

|          | Percentage reduction | 37.04%     | 37.04% | 37.04% | 24.19%              | 0.86%               |

| Table III: Compa | rison with | other work |

|------------------|------------|------------|

|------------------|------------|------------|

| Bit size | Parameters              | Ref. [5] | This work |

|----------|-------------------------|----------|-----------|

| 200      | Power (mW)              | 13.598   | 0.250     |

| 8-Bit    | Delay(ns)               | 2.094    | 2.487     |

|          | Area (µm <sup>2</sup> ) | 952.343  | 542.485   |

|          | Power (mW)              | 29.311   | 2.241     |

| 16-Bit   | Delay (ns)              | 2.450    | 5.014     |

|          | Area (µm <sup>2</sup> ) | 1901.093 | 1060.01   |

#### 5. Conclusion

A 16-bit CSA is implemented in this paper using XOR based 1-bit full adder as a building block. The schematic has been designed in DSCH software and synthesized using 90 nm CMOS technology. The layout has been created and simulated in Micro wind software. From the simulation result 20.40% reduction in power consumption, 9.41% reduction in area and

2.01% reduction in delay have been achieved for an XOR-based 16-bit CSA than conventional CSA. Also 37.04% reduction in gate count and 24.19% current reduction were found.

# References

[1] Vaigandla, K. K., & Venu, D. N. (2021). A survey on future generation wireless communications-5G: multiple access techniques, physical layer security, beamforming approach. Journal of Information and Computational Science, 11(9), 449-474.

[2] Venu, D., Arun Kumar, A., & Vaigandla, K. K. (2022). Review of Internet of Things (IoT) for Future Generation Wireless Communications. International Journal for Modern Trends in Science and Technology, 8(03), 01-08.

[3] Sujith, A. V. L. N., Swathi, R., Venkatasubramanian, R., Venu, N., Hemalatha, S., George, T., & Osman, S. M. (2022). Integrating nanomaterial and high-performance fuzzy-based machine learning approach for green energy conversion. Journal of Nanomaterials, 2022, 1-11.

[4] Venu, N., & Anuradha, B. (2013, December). Integration of hyperbolic tangent and Gaussian kernels for fuzzy C-means algorithm with spatial information for MRI segmentation. In 2013 Fifth International Conference on Advanced Computing (ICoAC) (pp. 280-285). IEEE.

[5] Vaigandla, K. K., & Venu, D. N. (2021). Ber, snr and papr analysis of ofdma and sc-fdma. GIS Science Journal, ISSN, (1869-9391), 970-977.

[6] Venu, N. (2014, April). Performance and evalution of Guassian kernals for FCM algorithm with mean filtering based denoising for MRI segmentation. In 2014 International Conference on Communication and Signal Processing (pp. 1680-1685). IEEE.

[7] Karthik Kumar Vaigandla, D. (2021, November). Survey on Massive MIMO: Technology, Challenges, Opportunities and Benefits. YMER, 271-282.

[8] Venu, N., & Anuradha, B. (2015). Multi-Kernels Integration for FCM algorithm for Medical Image Segmentation Using Histogram Analysis. Indian Journal of Science and Technology, 8(34), 1-8.

[9] Venu, N., Yuvaraj, D., Barnabas Paul Glady, J., Pattnaik, O., Singh, G., Singh, M., & Adigo, A. G. (2022). Execution of Multitarget Node Selection Scheme for Target Position Alteration Monitoring in MANET. Wireless Communications and Mobile Computing, 2022.

[10] Venu, N., Swathi, R., Sarangi, S. K., Subashini, V., Arulkumar, D., Ralhan, S., & Debtera, B. (2022). Optimization of Hello Message Broadcasting Prediction Model for Stability Analysis. Wireless Communications & Mobile Computing (Online), 2022.

[11] Venu, D. N. (2015). Analysis of Xtrinsic Sense MEMS Sensors. International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering , 4 (8), 7228-7234.

[12] Venu, N., & Anuradha, B. (2013). A novel multiple-kernel based fuzzy c-means algorithm with spatial information for medical image segmentation. International Journal of Image Processing (IJIP), 7(3), 286.

[13] Nookala Venu, A. (2018). Local mesh patterns for medical image segmentation. Asian Pacific Journal of Health Sciences, 5(1), 123-127.

[14] Venu, N., & Anuradha, B. (2013). PSNR Based Fuzzy Clustering Algorithms for MRI Medical Image Segmentation. International Journal of Image Processing and Visual Communication, 2(2), 01-07.

[15] Thouti, S., Venu, N., Rinku, D. R., Arora, A., & Rajeswaran, N. (2022). Investigation on identify the multiple issues in IoT devices using Convolutional Neural Network. Measurement: Sensors, 24, 100509.

[16] Venu, N., Revanesh, M., Supriya, M., Talawar, M. B., Asha, A., Isaac, L. D., & Ferede, A. W. (2022). Energy Auditing and Broken Path Identification for Routing in Large-Scale Mobile Networks Using Machine Learning. Wireless Communications and Mobile Computing, 2022.

[17] Kesavaiah, D. C., Goud, T. R., Rao, Y. S., & Venu, N. (2019). Radiation effect to MHD oscillatory flow in a channel filled through a porous medium with heat generation. Journal of Mathematical Control Science and Applications, 5(2), 71-80.

[18] Nookala Venu, B. A. (2015). Medical Image Segmentation Using Kernal Based Fuzzy C-Means Algorithm. International Journal of Engineering Innovation & Research , 4 (1), 207-212.

[19] Nookala Venu, D., Kumar, A., & Rao, M. A. S. (2022). BOTNET Attacks Detection in Internet of Things Using Machine Learning. NeuroQuantology, 20(4), 743-754.

[20] Venu, N., & Anuradha, B. (2014, February). Multi-Hyperbolic Tangent Fuzzy C-means Algorithm for MRI Segmentation. In Proceedings of International Conference on Advances in Communication, Network and Computing (CNC-2014), Elsevier (pp. 22-24).

[21] Nookala Venu, S. W. (2022). A Wearable Medicines Recognition System using Deep Learning for People with Visual Impairment. IJFANS, 12(1), 2340-2348.

[22] Nookala Venu, G. R. (2022). Smart Road Safety and Vehicle Accidents Prevention System for Mountain Road. International Journal for Innovative Engineering Management and Research , 11 (06), 209-214.

[23] Nookala Venu, D., Kumar, A., & Rao, M. A. S. (2022). Smart Agriculture with Internet of Things and Unmanned Aerial Vehicles. NeuroQuantology, 20(6), 9904-9914.

[24] Nookala Venu, D., Kumar, A., & Rao, M. A. S. (2022). Internet of Things Based Pulse Oximeter For Health Monitoring System. NeuroQuantology, 20(5), 5056-5066.

[25] Venu, D. N. DA (2021). Comparison of Traditional Method with watershed threshold segmentation Technique. The International journal of analytical and experimental modal analysis, 13, 181-187.

[26] Dr.Nookala Venu, D. K. (2022). Investigation on Internet of Things (IoT):Technologies, Challenges and Applications in Healthcare. International Journal of Research , XI (II), 208-218.

[27] Kesavaiah, D. C., Goud, T. R., Venu, N., & Rao, Y. S. (2021). MHD Effect on Convective Flow of Dusty Viscous Fluid with Fraction in a Porous Medium and Heat Generation. Journal of Mathematical Control Science and Applications, 7(2).

[28] Babu, K. R., Kesavaiah, D. C., Devika, B., & Venu, D. N. (2022). Radiation effect on MHD free convective heat absorbing Newtonian fluid with variable temperature. NeuroQuantology, 20(20), 1591-1599.

[29] Kesavaiah, D. C., Ahmed, M., Reddy, K. V., & Venu, D. N. (2022). Heat and mass transfer effects over isothermal infinite vertical plate of Newtonian fluid with chemical reaction. NeuroQuantology, 20(20), 957-967.

[30] Reddy, G. B., Kesavaiah, D. C., Reddy, G. B., & Venu, D. N. (2022). A note on heat transfer of MHD Jeffrey fluid over a stretching vertical surface through porous plate. NeuroQuantology, 20(15), 3472-3486.

[31] Chenna Kesavaiah, D., Govinda Chowdary, P., Rami Reddy, G., & Nookala, V. (2022). Radiation, radiation absorption, chemical reaction and hall effects on unsteady flow past an isothermal vertical plate in a rotating fluid with variable mass diffusion with heat source. NeuroQuantology, 20(11), 800-815.

[32] Kesavaiah, D. C., Prasad, M. K., Reddy, G. B., & Venu, N. (2022). Chemical Reaction, Heat and Mass Transfer Effects on MHD Peristaltic Transport in A Vertical Channel Through Space Porosity And Wall Properties. NeuroQuantology, 20(11), 781-794.

[33] Kesavaiah, D. C., Reddy, G. B., Kiran, A., & Venu, D. N. (2022). MHD effect on boundary layer flow of an unsteady incompressible micropolar fluid over a stretching surface. NeuroQuantology, 20(8), 9442-9452.

[34] Kesavaiah, D. C., Chowdary, P. G., Chitra, M., & Venu, D. N. (2022). Chemical reaction and MHD effects on free convection flow of a viscoelastic dusty gas through a semi infinite plate moving with radiative heat transfer. NeuroQuantology, 20(8), 9425-9434.

[35] Mr.RadhaKrishna Karne, M. M. (2022). Applications of IoT on Intrusion Detection System with Deep Learning Analysis. International Jourfor Innovative Engineering and Management Research, 11 (06), 227-232.

[36] Venu, N., & Anuradha, B. (2015). Two different multi-kernels for fuzzy C-means algorithm for medical image segmentation. Int. J. Eng. Trends Technol.(IJETT), 20, 77-82.

[37] Kesavaiah, D. C., Goud, T. R., Venu, N., & Rao, Y. S. (2017). Analytical Study on Induced Magnetic Field with Radiating Fluid over a Porous Vertical Plate with Heat Generation. Journal of Mathematical Control Science and Applications, 3(2).

[38] Dr. Nookala Venu, D. A. (2022, March). Routing and Self-Directed Vehicle Data Collection for Minimizing Data Loss in Underwater Network. IJFANS International Journal of Food and Nutritional Sciences, 170-183.

[39] Dr. Nookala Venu, D. A. (2022). Fuzzy Based Resource Management Approach for the Selection of Biomass Material. IJFANS International Journal of Food and Nutritional Sciences, 12 (2), 83-97.

[40] Ravindra Kumar Agarwal, D. S. (2022). A Novel Dates Palm Processing and Packaging Management System based on IoT and Deep Learning Approaches. IJFANS International Journal of Food and Nutritional Sciences , 11 (8), 1139-1151.

[41] Manthur Sreeramulu Manjunath, P. K. (2022). An Enhanced Machine Learning Approach For Identifying Paddy Crop Blast Disease Management Using Fuzzy Logic. IJFANS International Journal of Food and Nutritional Sciences , 11 (8), 1152-1163.

[42] K.P.Senthilkumar, K. C. (2022). Machine Learning Based Analysis and Classification of Rhizome Rot Disease in Turmeric Plants. IJFANS International Journal of Food and Nutritional Sciences , 11 (8), 1179-1190.

[43] Sowmya Jagadeesan, B. B. (2022). A Perishable Food Monitoring Model Based on IoT and Deep Learning to Improve Food Hygiene and Safety Management. IJFANS International Journal of Food and Nutritional Sciences , 11 (8), 1164-1178.

[44] Nookala Venu, S. K. (2022). Machine Learning Application for Medicine Distribution Management System. IJFANS International Journal of Food and Nutritional Sciences , 11 (1), 2323-2330.

[45] Reddy, A. V., Kumar, A. A., Venu, N., & Reddy, R. V. K. (2022). On optimization efficiency of scalability and availability of cloud-based software services using scale rate limiting algorithm. Measurement: Sensors, 24, 100468.

[46] D. Chenna Kesavaiah, T. Ramakrishna Goud, Y. V. Seshagiri Rao, Nookala Venu (2019): Radiation effect to MHD oscillatory flow in a channel filled through a porous medium with heat generation, Journal of Mathematical Control Science and Applications, Vol. 5 (2), pp. 71-80.

[47] Venu, D. N. (2022). Smart Agriculture Remote Monitoring System Using Low Power IOT Network. IJFANS International Journal of Food and Nutritional Sciences, 11 (6), 327-340.

[48] Venu, D. N. (2022). IOT Surveillance Robot Using ESP-32 Wi-Fi CAM & Arduino. IJFANS International Journal of Food and Nutritional Sciences , 11 (5), 198-205.

[49] Nookala Venu, N. S. (2022). Study and Experimental Analysis on FBMC and OFDM. International Journal for Innovative Engineering and Management Research,11 (6), 49-53.

[50] Sandhya rani B, S. K. (2022). Vehicle Fuel Level Monitor and Locate the Nearest Petrol Pumps using IoT. International Journal for Innovative Engineering and Management Research , 11 (06), 233-240.

[51] Nookala Venu, K. A. (2022). Face Mask Detection System Using Python Open CV, International Journal for Innovative Engineering and Management Research, 11 (6), 28-32.

[52] Nookala Venu, V. M. (2022). Alcohol Detection and Engine Locking System. International Journal for Innovative Engineering and Management Research , 11 (06), 157-160.

[53] Nookala Venu, C. B. (2022). Wireless Night Vision Camera on War Spying Robot. International Journal for Innovative Engineering and Management Research , 11 (06), 123-128.

[54] Venu, D. N. (2022). IOT Based Enabled Parking System in Public Areas. IJFANS International Journal of Food and Nutritional Sciences, 11 (4), 162-174.

[55] Venu, D. N. (2022). IOT Based Speech Recognition System to Improve the Performance of Emotion Detection. IJFANS International Journal of Food and Nutritional Sciences, 11 (3), 92-102.

[56] Dr.Nookala Venu, M. S. (2018). Local Maximum Edge Binary Patterns for Medical Image Segmentation. International Journal of Engineering and Techniques, 4 (1), 504-509.

[57] Venu, N., & Anuradha, B. (2016). Multi-hyperbolic tangent fuzzy c-means algorithm with spatial information for MRI segmentation. International Journal of Signal and Imaging Systems Engineering, 9(3), 135-145.

[58] Venu, N., & Anuradha, B. (2015). Hyperbolic Tangent Fuzzy C-Means Algorithm with Spatial Information for MRI Segmentation. International Journal of Applied Engineering Research, 10(7), 18241-18257.

[59] Venu, N., & Anuradha, B. (2015, April). Two different multi-kernels integration with spatial information in fuzzy C-means algorithm for medical image segmentation. In 2015 International Conference on Communications and Signal Processing (ICCSP) (pp. 0020-0025). IEEE.

[60] Nookala Venu, B. (2015). MRI Image Segmentation Using Gaussian Kernel Based Fuzzy C-Means Algorithm. International Journal of Electronics Communication and Computer Engineering , 6 (1), 140-145.

[61] Venu, N., & Anuradha, B. (2015). Evaluation of Integrated Hyperbolic Tangent and Gaussian Kernels Functions for Medical Image Segmentation. International Journal of Applied Engineering Research, 10(18), 38684-38689.

[62] Anita Tuljappa, V. N. (2022). Dufour and Chemical Reaction Effects on Two Dimensional incompressible flow of a Viscous fluid over Moving vertical surface. NeuroQuantology, 63-74.

[63] Ch. Achi Reddy, V. N. (2022). Magnetic Field And Chemical Reaction Effects on Unsteady Flow Past A Stimulate Isothermal Infinite Vertical Plate. NeuroQuantology, 20 (16), 5360-5373.

[64] Sowmya Jagadeesan, M. K. (2022). Implementation of an Internet of Things and Machine learning Based Smart Medicine Assistive System for Patients with Memory Impairment. IJFANS International Journal of Food and Nutritional Sciences, 1191-1202.

[65] Venu, D. N. (2023). Design Analysis and Classification of Digital Transmission Based Composite Relay and Artificial Neural Network Approach. IJFANS International Journal of Food and Nutritional Sciences , 12 (1), 680-63.

[66] Venu, D. N. (2023). Biomass Studies on Pyrolysis of Sugarcane Bagasse and Cashew Nut Shell for Liquid Fuels. IJFANS International Journal of Food and Nutritional Sciences, 11 (1), 695-706.

[67] Venu, D. N. (2023). Synthesis and Study on Feasibility of Ethanol Production from Leachate of Pretreatment of Sugarcane Bagasse. IJFANS International Journal of Food and Nutritional Sciences , 12 (1), 707-715.

[68] Venu, D. N. (2022). Design and Performance Analysis of Super Critical Fluid Extraction for SC-CO2. IJFANS International Journal of Food and Nutritional Sciences , 11 (12), 3854-3865.

[69] Venu, D. N. (2022). Supercritical Fluid Evaluation and Extraction of Phenol from Sugarcane Bagasse Pyrolysis Oil. IJFANS International Journal of Food and Nutritional Sciences , 11 (12), 3866-3876.

[70] Sandhya rani, D. V. (2022). IOT Based Smart Irrigation System Using Node MCU. International Journal For Innovative Engineering and Management Research , 11 (6), 100-106.

[71] Dr.Nookala Venu, A. E. (2022). Low Power Area Efficient ALU with Low Power Full Adder. International Journal For Innovative Engineering and Management Research , 11 (06), 167-170.

[72] Nookala Venu, B.Anuradha"Brain MRI Medical Image Segmentation Using Fuzzy Based Clustering Algorithms", International Journal of Engineering Trends and Technology (IJETT), V22 (2), 83-88 April 2015. ISSN: 2231-5381. www.ijettjournal.org. published by seventh sense research group.

[73] Dr. Nookala Venu, D. K. (2023). Implementation of Hello Time Gaps Tracking Scheme for Network Stability Analysis in MANET. European Chemical Bulletin , 12 (8), 5011-5026.

[74] Ch.Shashi Kumar, K. R. (2023). Chemical Reaction and Hall Effects on Unsteady Flow Past an Isothermal Vertical Plate in a Rotating Fluid with Variable Mass Diffusion. European Chemical Bulletin, 12 (8), 4991-5010.

[75] Venu, D. N. (2022). Classification Analysis for Local Mesh Patterns Using Medical Image Segmentation. IJFANS International Journal of Food and Nutritional Sciences,11 (12), 5232-5241.

[76] Venu, D. N. (2022). PSNR Based Levels Evaluation of FCM Algorithm with Peak and Valley Filtering Based Brain Images. IJFANS International Journal of Food and Nutritional Sciences, 11 (12), 5242-5253.

[77] Venu, D. N. (2023). Segmentation Analysis for Local Maximum Edge Binary Patterns using Medical Images. IJFANS International Journal of Food and Nutritional Sciences, 12 (1), 917-927.

[78] Venu, D. N. (2023). PSNR Based Evalution of Spatial Guassian Kernals For FCM Algorithm with Mean and Median Filtering Based Denoising for MRI Segmentation. IJFANS International Journal of Food and Nutritional Sciences, 12 (1), 928-939.

[79] Venu, D. N. (2022). Multi Guassian Kernals for FCM Algorithm with Mean and Peak-Valley-Kernal Filtering Based Denoising for MRI Segmentation Using PSNR Analysis. IJFANS International Journal of Food and Nutritional Sciences, 11 (11), 1965-1976.

[80] Dr.A.Arun Kumar, D. N. (2023). Enhanced Security Packet Acceptance for Target Position Alteration using Multi Accepter Scheme Assigning Algorithm in MANET. European Chemical Bulletin, 12 (8), 7003-7018.

[81] Dr.A.Arun Kumar, D. N. (2023). Analysis and Enhancement of Energy Auditing Routing for Identification of Broken Paths in Mobile Adhoc Networks. European Chemical Bulletin , 12 (8), 7019-7034.

[82] Dr. Sowgani Ramakrishna, D. A. (2023). Computational Mathematical Modelling of Radiative Chemical Reaction and Hall Effects on unsteady flow past an Isothermal Vertical Plate with radiation and Heat Absorption. European Chemical Bulletin , 12 (8), 8436-8452.